|

個人情報保護方針 お支払いについて お問い合わせ |

|

|

FPGAと歩んで35年 FPGAが商用の半導体製品として最初に発表されたのは1985年11月だそうです。FPGAとは"Field Programmable Gate ArrayPLD"の略で、PLD(Programmable Logic Device)つまりプログラム可能な回路ということになります。PLDとの出会いは大学の研究室でした。当時はデバイス内のPROMのフューズを焼き切って回路のプログラムを行う1発勝負のデバイスでしたが、画期的なものができた。世の中が変わるだろうと思ったものです。 その後、メーカーに入社した私は当時ソフトウェアでは処理が間に合わないが、ゲートアレイ(専用IC)を作って採算が取れるほど数が出ない製品で、当時アルテラが始めて量産用として投入してて来たFPGAを採用して、国内有名メーカーのインクジェット素子の制御を行いました。当時のFPGAはASIC(特定用途向けIC)の試作や高価な交換機などに用いられ数万円していましたが、使用したデバイスは数千円というものでした。その後、シリコンバレーでスタンダードセル方式のICの設計にも携わり、より深くICの性質や設計上の注意点などを学ぶことになります。これがFPGAを設計するうえでも大変良い経験となっていることはいうまでもありません。FPGAというとVelilogやVHDLといった論理記述言語で書かれ、コンパイルすれば問題なく動くと思われがちですが、コンパイル後は回路になります。つまり回路に適した論理でないと意図していない回路や、無駄に回路規模のとても大きな回路、あるいは高速な動作が難しい遅い回路などができてしまいます。FPGAの書き換えることができるという利点を生かしつつ、回路であるということを忘れないことが設計の肝ではないかと考えています。 |

|

|

ソフトウェアか回路か この業界にいていつも思うのは、ソフトウェアとハードウェアの技術者の対立です。ソフトウェア技術者はなんでもソフトウェアでやりたがります。ハードウェア技術者はハードウェアはハードウェアでやるのがベストだと主張しがちです。しかし、特に組み込み器機においては、どちらがベターかというのは状況によって異なることが多いです。たとえば頻繁に変更して使用するような用途でしたらソフトウェアのほうが変更も検証もやりやすいです。しかし、高速な処理が必要な場合には、ソフトウェアでやるほうが高くつくことも事実です。ソフトウェアはCPUでプログラムを用いて逐次的に処理します。つまりマルチコアのプロセッサを用いる場合を除けば、一度に1つのことしかできません。原理的に言えば、例えば加算をしている間は他の回路は止まっています。しかし、ハードウェアは基本的にすべての回路を同時に動かすように設計できます。流れ作業で行うことができる処理は、1つの処理をした後に次の回路に渡すということを繰り返すことにより、非常に多くの並列処理を行うことができます。これは非常に大きなメリットです。FPGAを用いて信号を処理するうえで、フィルタをかけたり、微分したり、特定の信号を検出したりする処理がこれに該当します。A/Dコンバータなどでデジタル化した大量の信号をそのままPCに転送して、PCの有り余るパワーで処理する方法もありますが、一方で回路のほうでデータを処理して、欲しい部分だけを取り出して保管したり、欲しい周波数成分だけを取り出してデータ量を大幅に圧縮したりもできます。データ量を減らせば長時間の測定も可能になり、容易に設置と取り出しができないような、地下深くや海の底といった場所での測定に向いたシステムも作れたりします。また、消費電力の面でも効率的な処理は有利になります。こういった特殊な用途においてますますFPGAは活躍していくと思っています。 |

|

FPGA設計の流れ お客様から提示される仕様の詳細度合い、難易度、使用するFPGAやツールによって内容は異なってきますが、おおむね下記の順番で設計を行います。一口に回路設計と言っても、RTL(回路記述言語)を使って回路を記載する作業は全体の1割にも満たないことが多く、ほとんどの時間は検証に当てられます。たったこれだけの設計にこんなに費用がかかるのかといわれることがありますが、実際に多くの手間がかかることを理解していただければと思います。

|

|

設計事例 GroveDesignServiceのお客様は各種製造装置、検査装置、地震計、海洋、宇宙など他分野にわたります。企業様、大学様、産学共同などの機構様にも納入しています。基本的にお客様の情報や具体的な用途、製品名などを公開することはできませんが、ここではお客様や製品が特定できない範囲で紹介したいと思います

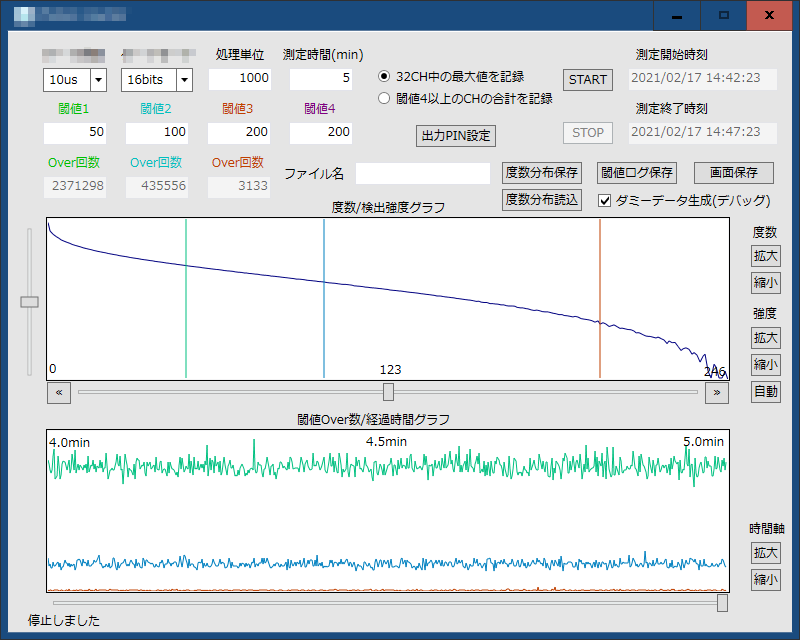

・データー収集・測定

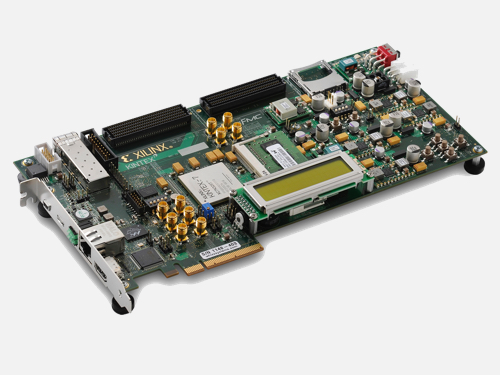

・PCとの通信方法  また、高速に通信したい場合にはPCIexpressが用いられます。PCI Express 2.0で1レーンあたりで双方向1GB/s(1方向500MB/s)と高速で、x4ですと4GB/sとUSB3.0よりも高速となっています。PCIexpressはPCの拡張スロットに装着されます。WindowsまたはLinuxのドライバが必要になります。FPGAメーカーから提供されるサンプルドライバを用いることもあれば、新たにドライバを作成することもあります。たいていの場合、FPGAと通信するCUI(コマンドインターフェイス)またはGUI(グラフィカルインターフェイス)のサンプルプロジェクトまで納品することが多いです。お客様のほうでこれをベースにカスタマイズするか、手に負えない場合にはこちらでも引き受けます。

・画像処理

・メジャーではないFPGAメーカーにも対応   |

|